# Agilent E2920 PCI Timing Check using the Agilent E2920 PCI Series Exerciser/Analyzer

Application Note

#### Introduction

Until now, verifying that timing in 33 MHz 64-bit PCI designs met the setup and hold specification, required either very tedious measurements of all signals with a digital storage oscilloscope (DSO) or a very high speed logic analyzer, which is very costly. The timing check feature of the E2920 PCI Series Exerciser/Analyzer simultaneously monitors all 87 synchronous bused PCI signals for both setup and hold timing violations and identifies suspect individual signals. It works with your DSO to speed up the timing verification process not only by quickly telling you which signals are violating timing, but also triggering your scope *when* a timing violation occurs.

#### **PCI** Timing parameters

The PCI electrical specifications call for very tight AC timing characteristics. Even though the devices that are used in your design meet the PCI specifications, system design problems such as crosstalk or ground bounce lead to a need to verify your system timing.

1. The E2920 series with Timing Check capability includes the E2925B, E2926A, E2926B, E2927A, E2928A, and E2940A.

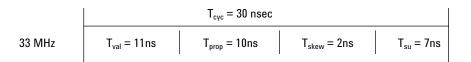

The PCI specification calls for timing parameters outlined in figure 1.

All times shown in the timing budget in figure 1 are fixed by the specification, except for  $T_{prop}$ .  $T_{prop}$  is a computed value, based on the total timing budget, so factors that affect propagation time such as output driver characteristics, trace length (including trace length on adapter cards), number of loads, affect this system parameter. Since only some of these parameters are fully under control of the system designer, it is not possible to fully guarantee input timing under all circumstances. This makes it important to characterize and measure the PCI bus for timing violations.

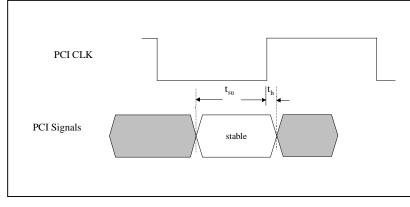

Fundamentally, it is the input timing specifications (table 1),  $T_{su}$  and  $T_{h}$ , which must be met to insure proper operation. An output must drive its signal to all other devices on the PCI

#### **Key Features**

- Setup and hold time violation checking across 87 synchronous, bused signals

- Edge and glitch detection within the setup/hold window

- User adjustable window size within +/- 2 ns of both the PCI specification setup and hold time in 250 ps steps (total of up to 4 ns adjustment)

- Typical accuracy of +/- 250 ps at the PCI specification points

- Operation from 29 MHz to 35 MHz

- Generates a trigger output that can be used by a scope as a trigger

- Maskable selection of individual signals allows triggering on a single signal

- Protocol sensitive, so it doesn't operate during turn-around cycles

Figure 1. Total Timing Budget — 33 MHz

bus to provide a stable input prior to the next rising clock edge (Tsu) and assure its stability until that following clock edge (Th). To measure if the system meets its setup time requires special measurement techniques, since the signal being measured happens before its point of reference (the PCI clock).

| Speed  | Setup Time<br>(nsec min.) | Hold Time<br>(nsec min) |

|--------|---------------------------|-------------------------|

| 33 MHz | 7                         | 0                       |

#### Table 1: PCI Input Timing Specifications – Bused Signals

#### **Challenges to measure**

Measuring setup and hold time on 87 signals with a reasonable amount of accuracy requires either lots of time or lots of money. Using a DSO with a small channel count is a very effective but also very tedious method to characterize and measure setup and hold times for many signals. With one channel needed to probe the PCI clock, most scopes only allow up to three additional signals to be probed at a time. The DSO is an excellent tool to characterize the signal parametrics and to determine why a setup or hold violation has occurred, but its limited channel count makes it impractical to efficiently identify signals with timing violations.

Another choice to check for setup and hold violations is a high-speed timing analyzer. Timing analyzers have the advantage of viewing the entire bus, which allows simultaneous measurement of every signal with respect to the clock. The timing analyzer however, does not provide usable information about the signal parametric properties as a DSO does. It essentially has a one-bit D/A converter on every channel, so it is impossible to view actual signal characteristics with it, such as rise time, ringing, reflections, overshoot, etc.

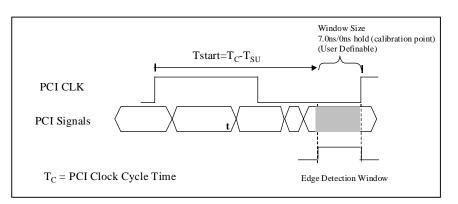

A logic analyzer also needs special circuitry to detect edges or glitches, since a valid setup time means that there is an absence of signal transitions for 7 ns prior to the rising edge of the PCI clock. But how does the analyzer know when the clock edge will occur since it is after the interval of time we are interested in? The

answer is that a setup time is measured starting N nanoseconds after the previous clock edge. Then it is simply a matter of calculating the cycle time and starting the edge detection circuit the appropriate time after the prior clock. This however, presents a need for more circuitry. Now the logic analyzer must be capable of accurately measuring the cycle time so it can calculate the correct time to start the edge/glitch detection circuitry. Additionally, the edge/glitch detection circuitry must be capable of being gated on and off, since it should only detect transitions during a small portion of the total cycle time. Only specially equipped logic analyzers are capable of this, but they either suffer from too small a channel count or a very high a price.

While neither the DSO nor the Logic analyzer provides an optimal solution, the DSO is the correct tool to visualize a signal when a violation has occurred because it has very high timing accuracy and can provide insight into the actual phenomena that is causing the timing violation.

**Figure 2: PCI Timing Requirements**

#### **Timing check**

The Timing Check for the Agilent E2920 PCI Series operates simultaneously across all the PCI synchronous bused signals. This makes it an ideal companion to a DSO, which can be used to visualize the bad signal(s).

#### How it works

In order to measure setup time, which occurs prior to the reference signal, and hold time which is specified at 0ns with respect to the PCI clock, the timing check performs the following operations.

1. Measure the PCI clock frequency. The frequency is measured prior to the timing check being activated and is stored as a reference value. Prior to returning its status, the frequency is measured again and compared to the reference frequency. If they do not compare, the timing check is turned off indicating that a measurement is not possible since the clock frequency is not stable.

2. Get the user settings for the measurement window size. The default values are the actual PCI setup/hold specifications for the given bus frequency.

3. Adjust delay lines to start and stop the measurement window after the previous clock edge. This operation uses the information from steps 1 & 2 to determine the correct settings for the delay lines.

#### **The GUI Interface**

The timing check can be used either with the standard CAPI interface provided with the Agilent PCI Exerciser/ Analyzer or with the E2970A Analyzer Graphical User Interface. Both require software version R5.10.07 or greater.

When using the graphical user interface, the timing check window can be viewed using the main window menu Analyzer > Timing Check.... It is shown to the right in figure 4. On the left hand side of the window, all the PCI signals are listed individually along with twelve external trigger inputs that can simultaneously be measured. Associated with each signal is a *Mask* and Status field. The mask field allows individual signals to be enabled to provide a trigger capability when only that signal generates a timing violation. The status field shows one of three status values. A green **OK** indicates that there is no detected timing violation on that signal with the current setup and hold values. A yellow **ERROR** indication flags the occurrence of a timing violation, but that signal was masked off. This prevents a timing violation on this signal from generating a trigger condition. A red **ERROR** indication flags an unmasked timing violation.

The default measurement window size is set to the PCI 33 MHz timing specification. (7 nsec setup/0 ns hold). Variations of +/- 2 ns from the default values are possible in 250 psec steps. Press the *Edit...* button in the Timing Check window to modify the window size (figure 5). Selecting the *Manual* setting allows you to modify the setup/hold time values for the desired measurement window size.

| Mask<br>Enabled<br>Enabled<br>Enabled<br>Enabled<br>Enabled | Clear<br>Status<br>ERROR<br>ERROR<br>OK<br>OK                                          |

|-------------------------------------------------------------|----------------------------------------------------------------------------------------|

| Enabled<br>Enabled<br>Enabled<br>Enabled                    | ERROR<br>ERROR<br>OK                                                                   |

| Enabled<br>Enabled<br>Enabled                               | ERROR<br>OK                                                                            |

| Enabled<br>Enabled                                          | OK                                                                                     |

| Enabled                                                     |                                                                                        |

|                                                             | OK                                                                                     |

| Final Land                                                  | UK                                                                                     |

| Enabled                                                     | OK                                                                                     |

| Enabled                                                     | ERROR                                                                                  |

| Enabled                                                     | ERROR                                                                                  |

| Enabled                                                     | ERROR                                                                                  |

| Enabled                                                     | OK                                                                                     |

| Enabled                                                     | OK                                                                                     |

| Enabled                                                     | ERROR                                                                                  |

| Enabled                                                     | OK                                                                                     |

| Enabled                                                     | OK                                                                                     |

| Enabled                                                     | OK .                                                                                   |

|                                                             | nabled<br>nabled<br>nabled<br>nabled<br>nabled<br>nabled<br>nabled<br>nabled<br>nabled |

Figure 4. Timing Check Main Window

| 🖑 Timing Cl        | neck (E2926A        | - Offline) |                |

|--------------------|---------------------|------------|----------------|

| <u>File S</u> etup | <u>Signal H</u> elp |            |                |

| Status: Inval      | <u>E</u> nable All  |            |                |

| Signals violā      | Disable All         |            | Read from card |

| olynais viula      | ieu. 23             |            | Clear          |

Figure 5. Timing Check Adjustment Window

Another important control in the GUI is the *Signal* menu, to enable or disable all signals (figure 6). This control is useful when a signal or signals have shown a timing violation and you want to isolate a trigger condition on an individual signal. All signals can easily be masked off, then you can enable the individual signal that you want to trigger on.

#### How to use

After installing the PCI Exerciser/ Analyzer, start the GUI on your host platform (this could also be your DUT if you control the card through the PCI port). Follow the steps below to:

## Check for violations at the PCI specification values

1. From the Timing Check window, verify that the PCI timing specifications are selected for your bus speed.

2. Choose the *Signal-Enable All* menu to turn on all signals.

3. The timing check will run automatically. Run some programs that exercise the different masters in your DUT to verify that they all drive the bus with valid  $T_{val}$  timing.

4. Press the *Read from card* button in the Timing Check window to upload the timing check output. If a timing violation occurs, go to the procedure **Trigger on a timing violation**.

| Timing Check (E2926A                                    | Offline)       |

|---------------------------------------------------------|----------------|

| <u>File Setup Signal H</u> elp                          |                |

| Status: Inval <u>E</u> nable All<br><u>D</u> isable All | Read from card |

| Signals violated: 29                                    | Clear          |

Figure 6. Signal Menu—Timing Checker Main Window

#### **Determine PCI timing margins**

The timing check can be used to check your timing margins up to 2 ns greater than both the PCI specification's setup and hold times. For a 33 MHz PCI bus, this means that the setup time margin can be checked up to 9 nsec and hold time margin to +2 nsec after the rising edge of the clock.

1. Choose the **Signal > Enable All** menu to turn on all signals.

2. Press the *Edit...* button in the Timing Check window. Select the *Manual* button to allow the timing check window size to be edited. Change the setup and/or hold time to their maximum values to check for the widest timing margin.

3. The timing check will run automatically. Run some programs that exercise the different masters in your DUT to verify that they all drive the bus with valid  $T_{val}$  timing.

4. Press the *Read from card* button in the Timing Check window to upload the timing check output. If a timing violation occurs, go to the procedure **Trigger on a timing violation**.

5. If timing violations occur, you can modify the timing check window size to determine the amount of timing margin in your system.

#### Trigger on a timing violation

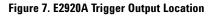

The full power of the timing check becomes available when it is used to trigger a DSO upon a timing violation. The timing check should first be used to identify which signal or signals are causing a timing violation. After this, it is appropriate to trigger a DSO when a "slow" signal is identified for probing.

1. In the timing check window, choose the *Signal->Disable All* menu to turn off all signals.

2. In the same window, select an individual signal to enable by clicking left mouse button when the cursor is over that signal name.

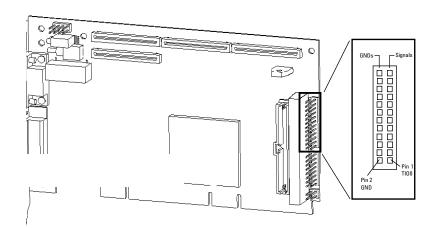

3. Connect the trigger input of your DSO to the **TIOO** (Trigger I/O 0) signal on the Agilent PCI Exerciser/ Analyzer. Refer to figure 7 for the location of this signal. Note that ground signals are on all 12 pins of the trigger I/O header to the left of each signal.

4. Probe the **signal of interest** and the **PCI CLK** signals on your DUT with two channels of your DSO.

5. Open the Command Line window in the E2926 GUI from the menu Windows-> Command Line.... Use the File->Run Script... menu to run "samples\gui\tmgchktr.cli". This command line script sets up the trigger I/O sequencer to generate a rising edge on TIOO when a timing violation has occurred.

6. Set your DSO to trigger on the external trigger input.

Figure 8. Typical Measurement Setup

|          | Universal Board   |                   | Universal Board |                   |                   |

|----------|-------------------|-------------------|-----------------|-------------------|-------------------|

| Pin      | Side B            | Side A            | Pin             | Side B            | Side A            |

|          | -12V              | TRST#             | 49              | M66EN             | AD[09]            |

| 2        | ТСК               | +12V              | 50              | KEYV              | VAY               |

| }        | Ground            | TMS               | 51              | KEYV              | VAY               |

|          | TDO               | TDI               | 52              | AD[08]            | C/BE[0]           |

|          | +5V               | +5V               | 53              | AD[07]            | +3.3V             |

| ;        | +5V               | INTA#             | 54              | +3.3V             | AD[06]            |

| ,        | INTB#             | INTC#             | 55              | AD[05]            | AD[04]            |

| }        | INTD#             | +5V               | 56              | AD[03]            | Ground            |

| )        | PRSNT1#           | Reserved          | 57              | Ground            | AD[02]            |

| 0        | Reserved          | +5V               | 58              | AD[01]            | ADIOO             |

| 1        | PRSNT2#           | Reserved          | 59              | $+V_{1/0}$        | +V <sub>1/0</sub> |

| 2        | KEYW              |                   | 60              | ACK64#            | REQ64#            |

| 3        | KEYW              |                   | 61              | +5V               | +5V               |

| 4        | Reserved          | Reserved          | 62              | +5V               | +5V               |

| 5        | Ground            | RST#              | 02              | KEYV              |                   |

| 6        | CLK               | +V <sub>1/0</sub> |                 | KEYV              |                   |

| 7        | Ground            | GNT#              | 63              | Reserved          | Ground            |

| 8        | REQ#              | Ground            | 64              | Ground            | C/BE[7            |

| 9        | +V <sub>1/0</sub> | Reserved          | 65              | C/BE[6]           | C/BE[5]           |

| 20       | AD[31]            | AD[30]            | 66              | C/BE[4]           | +V <sub>I/0</sub> |

| .u<br>21 | AD[31]<br>AD[29]  | +3.3V             | 67              | Ground            | PAR64             |

| 22       |                   |                   | 68              |                   |                   |

| 23       | Ground            | AD[28]            | 69              | AD[63]            | AD[62]            |

| 23<br>24 | AD[27]            | AD[26]            |                 | AD[61]            | Ground            |

| 24<br>25 | AD[25]            | Ground            | 70              | +V <sub>1/0</sub> | AD[60]            |

|          | +3.3V             | AD[24]            | 71<br>72        | AD[59]            | AD[58]            |

| 26       | C/BE[3]]#         | IDSEL             |                 | AD[57]            | Ground            |

| 27       | AD[23]            | +3.3V             | 73              | Ground            | AD[56]            |

| 28       | Ground            | AD[22]            | 74              | AD[55]            | AD[54]            |

| 29       | AD[21]            | AD[20]            | 75              | AD[53]            | +V <sub>I/0</sub> |

| 80       | AD[19]            | Ground            | 76              | Ground            | AD[52]            |

| 81       | +3.3V             | AD[18]            | 77              | AD[51]            | AD[50]            |

| 32       | AD[17]            | AD[16]            | 78              | AD[49]            | Ground            |

| 3        | C/BE[2]           | +3.3V             | 79              | +V <sub>I/0</sub> | AD[48]            |

| 4        | Ground            | FRAME#            | 80              | AD[47]            | AD[46]            |

| 5        | IRDY#             | Ground            | 81              | AD[45]            | Ground            |

| 6        | +3.3V             | TRDY#             | 82              | Ground            | AD[44]            |

| 37       | DEVSEL#           | Ground            | 83              | AD[43]            | AD[42]            |

| 88       | Ground            | STOP#             | 84              | AD[41]            | +3.3V             |

| 39       | LOCK#             | +3.3V             | 85              | Ground            | AD[40]            |

| 0        | PERR#             | SDONE             | 86              | AD[39]            | AD[38]            |

| 1        | +3.3V             | SBO#              | 87              | AD[37]            | Ground            |

| 2        | SERR#             | Ground            | 88              | +V <sub>I/0</sub> | AD[36]            |

| 3        | +3.3V             | PAR               | 89              | AD[35]            | AD[34]            |

| 4        | C/BE[1]#          | AD[15]            | 90              | AD[33]            | Ground            |

| 5        | AD[14]            | +3.3V             | 91              | Ground            | AD[32]            |

| 6        | Ground            | AD[13]            | 92              | Reserved          | Reserve           |

| 7        | AD[12]            | AD[11]            | 93              | Reserved          | Ground            |

| 8        | AD[10]            | Ground            | 94              | Ground            | Reserve           |

### PCI LocalBus Board Pinout Relevant Signals in Bold Face

| <b>Related Literature</b><br>E2920 Computer Verification Tools, PCI Series, | Pub. No.   | By internet, phone, or fax, get assistance<br>with all your test and measurement needs.    |  |

|-----------------------------------------------------------------------------|------------|--------------------------------------------------------------------------------------------|--|

| brochure                                                                    | 5968-3507E | Online Assistance<br>www.agilent.com/find/assist                                           |  |

| E2920 PCI Performance Multimedia CD                                         | 5965-5882E | Phone or Fax<br>United States:<br>(tel) 1 800 452 4844                                     |  |

| E2925B 32 bit, 33 MHz, E2926B 32/64 bit,<br>33 MHz PCI Exerciser & Analyzer | 5968-3501E | (ter) 1 000 432 4644<br>Canada:                                                            |  |

| E2940A CompactPCI Exerciser & Analyzer,                                     | 5500-5501E | (tel) 1 877 894 4414<br>(fax) (905) 206 4120                                               |  |

| data sheet                                                                  | 5968-1915E | Europe:<br>(tel) (31 20) 547 2323<br>(fax) (31 20) 547 2390                                |  |

| E2928A 32/64 bit 66 MHz PCI Exerciser & Analyzer,<br>data sheet             | 5968-3506E | Japan:<br>(tel) (81) 426 56 7832<br>(fax) (81) 426 56 7840                                 |  |

|                                                                             |            | Latin America:<br>(tel) (305) 269 7500<br>(fax) (305) 269 7599                             |  |

|                                                                             |            | Australia:<br>(tel) 1 800 629 485<br>(fax) (61 3) 9272 0749                                |  |

|                                                                             |            | New Zealand:<br>(tel) 0 800 738 378<br>(fax) (64 4) 495 8950                               |  |

| For more information visit us at:<br>www.agilent.com/info/pci_overview      |            | Asia Pacific:<br>(tel) (852) 3197 7777<br>(fax) (852) 2506 9284                            |  |

|                                                                             |            | Product specifications and descriptions in this document subject to change without notice. |  |

|                                                                             |            | Copyright © 1999, 2000 Agilent Technologies                                                |  |

Copyright © 1999, 2000 Agilent Technologies Printed in U.S.A. 7/005968-5816E